Western Digital est un fabricant bien connu notamment de disques durs. Pour leur opération, ces systèmes devenus très complexes nécessitent des microcontrôleurs évolués : l'époque où il fallait parquer soi-même les têtes du disque dur avant un déplacement est définitivement révolue

Pour ce faire, Western Digital reposait jusqu'il y a peu sur une foule d'architectures, notamment pour des raisons historiques (la technologie utilisée par les entreprises rachetées était gardée pour la suite du cycle de vie de la gamme) : ARM, MIPS ou encore ARC. L'année dernière, le fabricant a lancé un pavé dans la marre en annonçant qu'il se lançait dans la conception d'un processeur basé sur l'architecture RISC-V, qui fait beaucoup parler d'elle pour le moment de par son côté totalement ouvert. Grâce à ces nouveaux contrôleurs, Western Digital espère continuer à innover dans son domaine, les données.

Western Digital est un fabricant bien connu notamment de disques durs. Pour leur opération, ces systèmes devenus très complexes nécessitent des microcontrôleurs évolués : l'époque où il fallait parquer soi-même les têtes du disque dur avant un déplacement est définitivement révolue

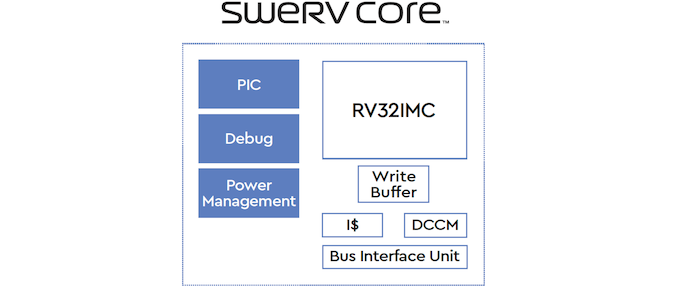

Pour ce faire, Western Digital reposait jusqu'il y a peu sur une foule d'architectures, notamment pour des raisons historiques (la technologie utilisée par les entreprises rachetées était gardée pour la suite du cycle de vie de la gamme) : ARM, MIPS ou encore ARC. L'année dernière, le fabricant a lancé un pavé dans la marre en annonçant qu'il se lançait dans la conception d'un processeur basé sur l'architecture RISC-V, qui fait beaucoup parler d'elle pour le moment de par son côté totalement ouvert. Grâce à ces nouveaux contrôleurs, Western Digital espère continuer à innover dans son domaine, les données.Ce processeur ne fait pas dans le dernier cri à tout point de vue : l'objectif n'est pas de copier ce qui se fait dans le monde x86 ou ARM, mais d'avoir un produit adapté aux applications prévues (Internet des objets, contrôleurs de mémoire flash ou de disques durs). Ainsi, SweVR est un cur trente-deux bits qui exécute les instructions dans l'ordre (contrairement à la majorité des processeurs à haute performance actuels, comme presque tous les curs x86 ou ARM : le processeur peut commencer à exécuter certaines instructions, par exemple pour récupérer des données, avant leur position dans le programme). La conception actuelle utilise un processus de fabrication à vingt-huit nanomètres et peut atteindre une fréquence de 1,8 GHz.

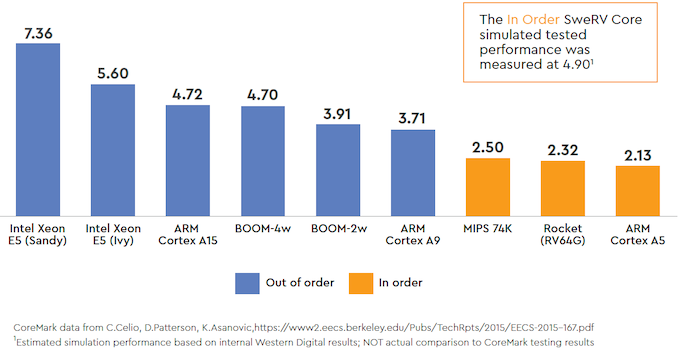

Il pourrait entrer en concurrence avec les ARM Cortex A15, des curs ARM à très faible consommation ; la différence principale est que, à fréquence égale, SweVR effectue plus de calculs par unité de temps. Plus précisément, Western Digital annonce un ratio de 4,9 points CoreMark par mégahertz, un peu plus qu'un Cortex A15 (4,72), mais avec une conception bien plus siple ; le processeur n'est pas si loin des processeurs x86 de précédente génération (comme les Ivy Bridge d'Intel, fabriqués dès 2012 sur un processus légèrement plus performants : ils atteignent 4,6 points par mégahertz). Il faut cependant remarquer que les performances de la concurrence ne sont pas estimées avec les compilateurs les plus à jour, par exemple, ais aussi que ceux de SweVR sont obtenus par simulation (et probablement sans trop d'optimisations, vu que le projet n'est pas si vieux ni mature).

Dans la lignée de l'architecture RISC-V, Western Digital envisage de proposer son cur SweRV sous licence libre début 2019, afin d'inciter d'autres à utiliser cette architecture. Pour le moment, on dispose d'un simulateur (sous licence GPL 3), ISS, qui permet déjà de tester des logiciels sur cette architecture sans forcément avoir un processeur sous la main. Cette étape est essentielle pour créer un environnement de développement dans un premier temps.

Source et images : Western Digital Reveals SweRV RISC-V Core, Cache Coherency over Ethernet Initiative.

Vous avez lu gratuitement 32 articles depuis plus d'un an.

Soutenez le club developpez.com en souscrivant un abonnement pour que nous puissions continuer à vous proposer des publications.

Soutenez le club developpez.com en souscrivant un abonnement pour que nous puissions continuer à vous proposer des publications.