Le futur des processeurs en général semble être du côté des pucettes, de petites briques fonctionnelles, toutes fabriquées indépendamment les unes des autres, puis rassemblées sur un interposeur pour former le processeur final. Toutes ces pucettes communiqueraient à l'aide d'un réseau interne au processeur. La DARPA prévoit ainsi de fabriquer des processeurs à la pointe de la technologie tout en utilisant des processus de fabrication plus vieux. AMD a proposé une technique de conception des accès au réseau pour éviter tout blocage, Intel un protocole et un bus pour former la moelle épinière de ces processeurs.

Le futur des processeurs en général semble être du côté des pucettes, de petites briques fonctionnelles, toutes fabriquées indépendamment les unes des autres, puis rassemblées sur un interposeur pour former le processeur final. Toutes ces pucettes communiqueraient à l'aide d'un réseau interne au processeur. La DARPA prévoit ainsi de fabriquer des processeurs à la pointe de la technologie tout en utilisant des processus de fabrication plus vieux. AMD a proposé une technique de conception des accès au réseau pour éviter tout blocage, Intel un protocole et un bus pour former la moelle épinière de ces processeurs.

Cependant, pour y arriver, il faut des techniques pour réaliser des interposeurs. Intel avait déjà proposé son EMIB (embedded multi-die interconnect bridge) y a quelques années, déjà mis à l'uvre notamment pour l'intégration de GPU AMD dans certains de ses processeurs. Maintenant, la même société annonce Foveros, une nouvelle manière de fabriquer des interposeurs. Les deux technologies se distinguent sur deux points : Foveros fonctionne en 3D et est actif. En 3D, car les pucettes peuvent se superposer librement, les connexions pourraient même passer à travers certaines pucettes. Actif, car l'interposeur n'est pas qu'une série de fils qui rejoignent les pucettes.

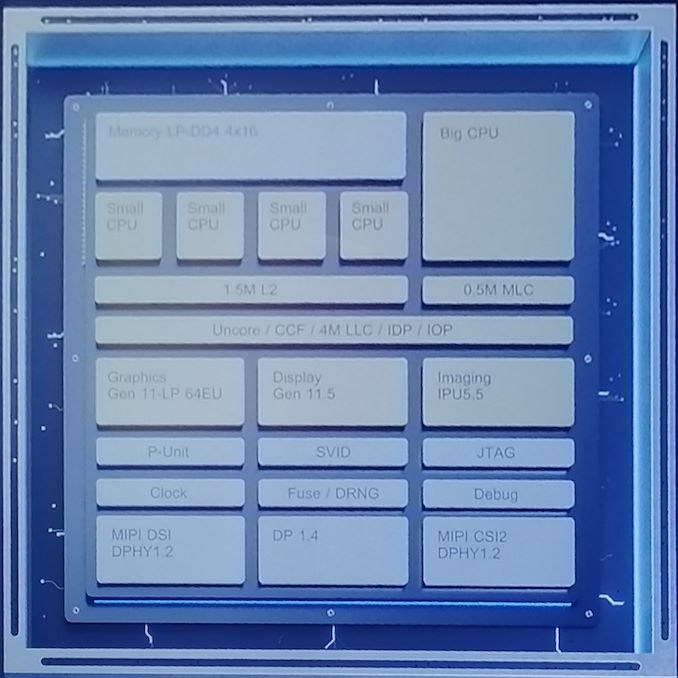

Ainsi, Intel se targue d'être en passe de fournir le premier processeur x86 hybride (à l'exception d'Intel Edison), à l'instar des processeurs big.LITTLE d'ARM. Un même processeur pourra ainsi contenir des curs totalement différents : par exemple, un cur Core (haute performance) et quatre curs Atom (très faible consommation). Un tel assemblage pourrait limiter sa consommation à deux milliwatts en pause.

Cette puce contient également un cache L2 pour le cur Core et un autre pour les quatre curs Atom. Tous partagent un cache L3 de quatre mégaoctets. La même puce contient également un contrôleur mémoire à quatre canaux, sans oublier un processeur graphique et un contrôleur DisplayPort.

Le tout dans un carré de douze millimètres de côté (un millimètre d'épaisseur).

L'idée principale derrière ce type de conception est que les différentes parties d'un processeur n'ont pas les mêmes besoins en termes de processus de fabrication. Par exemple, un processeur graphique intégré doit consommer très peu à un coût très faible ; un processeur graphique distinct a des contraintes moindres ; un processeur central pour ordinateur de bureau a surtout besoin de performance, pas tellement de prix.

Toutes ces pucettes pourront être fabriquées de manière distincte, sur le meilleur processus pour les besoins de cette fonctionnalité. Elles seront alors rassemblées sur un interposeur à haute densité, à l'aide de connexions à travers le silicium (TSV).

Sources et images : Intel Unveils Foveros, A Brand New Way To 3D Stack Chips With An Active Interposer, Intel unveils Foveros 3D chip stacking and new 10nm chiplets, Intel's Architecture Day 2018: The Future of Core, Intel GPUs, 10nm, and Hybrid x86.

Vous avez lu gratuitement 368 articles depuis plus d'un an.

Soutenez le club developpez.com en souscrivant un abonnement pour que nous puissions continuer à vous proposer des publications.

Soutenez le club developpez.com en souscrivant un abonnement pour que nous puissions continuer à vous proposer des publications.