Intel annonce son plan de route pour ses processeurs dès 2019,

Intel annonce son plan de route pour ses processeurs dès 2019,Sunny Cove apportera de sérieuses améliorations de performance

L'Intel Architecture Day, qui a eu lieu en début de semaine, était l'occasion pour Intel de présenter ses nombreuses avancées dans le domaine des processeurs. On a bien sûr eu droit à la présentation des avancées sur les processeurs graphiques, mais aussi sur les processeurs principaux. La prochaine génération de processeurs Intel Core, connue sous le nom de code d'Ice Lake (10e génération), devrait débarquer dès la mi-2019, avec des curs Sunny Cove (auparavant, le nom de code des curs de calcul n'était pas autant mis en avant : on a eu droit à des curs Skylake depuis 2015, par exemple). En 2020, on devrait voir arriver Willow Cove et, en 2021, Golden Cove. Tous ces processeurs/curs devraient être fabriqués sur le processus à 10 nm d'Intel, même s'il tarde à arriver.

Sunny Cove devrait représenter une grosse amélioration par rapport à Skylake, Intel résumant cette nouvelle itération comme "plus profonde, plus large et plus intelligente". Plus profonde, car ces curs exécuteront simultanément plus d'instructions par cycle d'horloge (en augmentant la taille des caches, pour trouver plus de parallélisme dans les instructions). Plus large, car ils effectueront plus d'instructions en parallèle (Sunny Cove pourra décoder cinq instructions en même temps, contre quatre avec Skylake). Plus intelligente, car les données seront mieux acheminées à travers le processeur (en diminuant la latence.

En même temps, cette nouvelle génération a été pensée avec les problèmes de sécurité comme Spectre, y compris la variante 3 ou encore L1TF. Aussi, Intel annonce une architecture qui se met plus facilement à l'échelle : la latence de communication entre curs devrait être moindre qu'actuellement (et augmenter moins vite avec le nombre de curs).

Cependant, ceci concerne la partie générique du processeur. Intel divise désormais sa stratégie en deux segments : la performance générique et la performance dans des applications spécifiques. Dans ce dernier point, on compte notamment de nouvelles instructions pour l'accélération des opérations des réseaux de neurones profonds ou la chaîne de blocs. Intel a par ailleurs confirmé l'arrivée des instructions AVX-512, dans la famille SIMD (exécution d'instructions sur des vecteurs de nombres, chaque opérande ayant une longueur de cinq cent douze bits d'où le nom).

Cette nouvelle génération apporte des caches bien plus grands ("deeper"

L'organisation générale entre le décodage des instructions et leur exécution a aussi été revue ("wider"

Au niveau de la mémoire, les processeurs utilisant des curs Sunny Clove pourront gérer une quantité de mémoire bien plus importante, grâce à une table de pagination à cinq niveaux. Ainsi, les adresses physiques en mémoire pourront utiliser jusque cinquante-deux bits (quatre bits de plus), pour monter jusqu'à quatre téraoctets de mémoire par processeur (les actuels sont limités à un téraoctet) ; les adresses virtuelles pourront utiliser jusque cinquante-sept bits.

En même temps, Intel propose deux mécanismes de sécurisation de la mémoire. MK-TME (multi-key total memory encryption) est une extension de TME, qui permet de chiffrer la mémoire : seul le processeur connaît la clé utilisée pour ce chiffrement ; MK-TME permet d'utiliser plusieurs clés dans un même processeur, par exemple une par utilisateur ou machine virtuelle (la clé est indiquée au niveau de chaque page de mémoire). UMIP (user-mode instruction prevention) empêche l'exécution de certaines instructions gérant la mémoire depuis un code utilisateur (par rapport au noyau), mais uniquement si cette sécurité est activée (il suffit d'une instruction).

Et les générations d'après ? Willow Cove (2020) devrait apporter une nouvelle conception des caches et des fonctionnalités de sécurité supplémentaires. Golden Cove (2021) devrait significativement améliorer la performance avec un seul fil d'exécution et en apprentissage profond ; le réseau et la 5G (donc la virtualisation dans les réseaux informatiques) sera aussi un axe de développement.

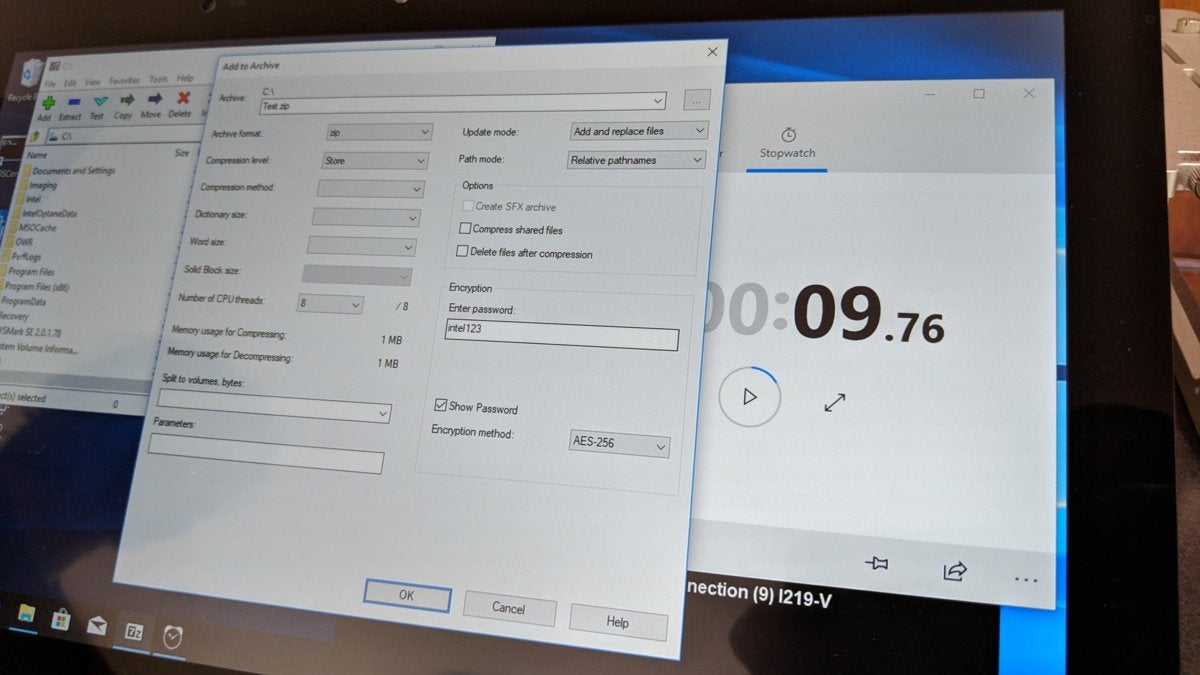

Tout ceci se fait presque sans chiffres sur la performance. Tout au plus a-t-on pu voir une démonstration de 7Zip avec chiffrement AES-256, qui permet de compresser septante-cinq pour cent plus vite que les processeurs actuels un résultat en bonne partie dû aux instructions prévues pour le chiffrement, peut-être aussi celles pour le chiffrement.

Sources et images : Intel Sunny Cove CPU Architecture and Next Generation Roadmap Revealed, Intel's Architecture Day 2018: The Future of Core, Intel GPUs, 10nm, and Hybrid x86, Surprise! Intel reveals 10nm Sunny Cove CPU cores that go deeper, wider, and faster.

Et vous ?

Qu'en pensez-vous ?

Qu'en pensez-vous ?

Vous avez lu gratuitement 367 articles depuis plus d'un an.

Soutenez le club developpez.com en souscrivant un abonnement pour que nous puissions continuer à vous proposer des publications.

Soutenez le club developpez.com en souscrivant un abonnement pour que nous puissions continuer à vous proposer des publications.

. Maintenant, il va y avoir de la vraie concurrence. En tout cas, je ne m'attend pas que leur prix sera raisonnable.

. Maintenant, il va y avoir de la vraie concurrence. En tout cas, je ne m'attend pas que leur prix sera raisonnable.