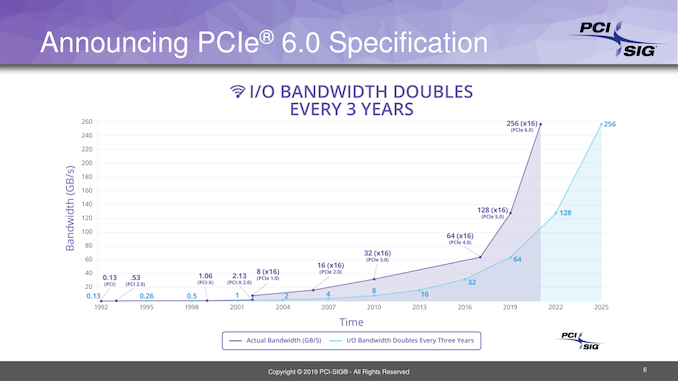

Le comité de normalisation de PCI Express (PCIe) enchaîne les annonces : la version 4.0 de la norme d'interconnexion de cartes a été annoncée en 2017 et commence son déploiement ce mois-ci (AMD lance des processeurs compatibles à destination du grand public, certaines de ses cartes graphiques gérant déjà la version 4.0 ; la 5.0 a été finalisée ce mois-ci. La 6.0 devrait doubler la bande passante disponible à l'horizon 2021 (c'est-à-dire soixante-quatre gigatransferts par seconde, soit cent deux cent cinquante-six gigaoctets par seconde sur un port PCIe x16).

Le comité de normalisation de PCI Express (PCIe) enchaîne les annonces : la version 4.0 de la norme d'interconnexion de cartes a été annoncée en 2017 et commence son déploiement ce mois-ci (AMD lance des processeurs compatibles à destination du grand public, certaines de ses cartes graphiques gérant déjà la version 4.0 ; la 5.0 a été finalisée ce mois-ci. La 6.0 devrait doubler la bande passante disponible à l'horizon 2021 (c'est-à-dire soixante-quatre gigatransferts par seconde, soit cent deux cent cinquante-six gigaoctets par seconde sur un port PCIe x16).

Les besoins en bande passante ne cessent d'évoluer dans les applications les plus intensives en calcul, la norme PCI Express se doit de rester à l'avant-plan et de proposer bien assez de bande passante pour ces utilisations. Cela devient de plus en plus important, vu le nombre de technologies construites par-dessus PCIe : NVMe est un protocole implémenté par les SSD par-dessus PCIe ; les protocoles CCIX (cache coherent interconnect for accelerators) et Intel CXL fournissent des interfaces d'interconnexion par-dessus PCIe. Ainsi, toute amélioration de PCIe profite aussi à ces utilisations.

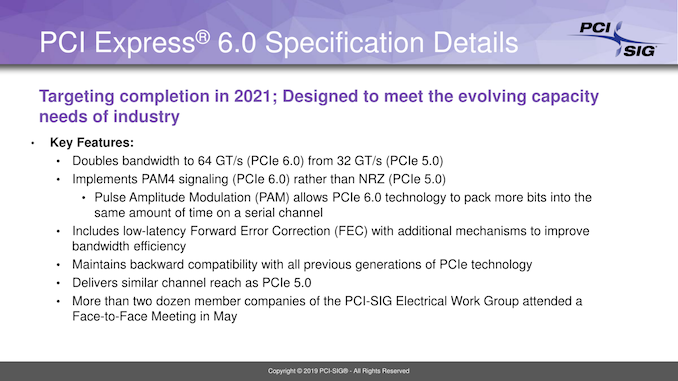

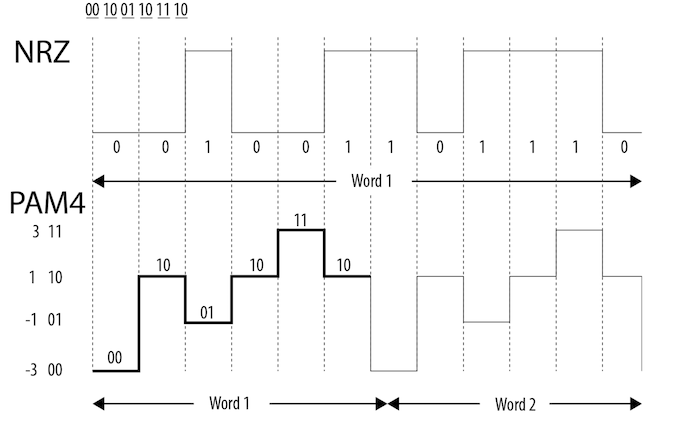

PCIe 6.0 apportera d'énormes nouveautés techniques par rapport aux versions précédentes, tout en gardant la rétrocompatibilité. PCIe 4.0 et 5.0 introduisent déjà des contraintes très fortes au niveau de la synchronisation : pour aller plus vite, PCIe 6.0 changera de modulation, en passant de NRZ à PAM4. La modulation concerne la manière d'encoder des zéros et des uns sur un canal analogique (une tension) : NRZ utilise seulement deux niveaux de tension, PAM4 quatre. Cela permet d'augmenter la quantité de données transférées sans augmenter la fréquence du signal.

PAM4 n'a rien de nouveau. Des variations sont utilisées pour Ethernet (dès la première version à cent mégabits par seconde) ou les signaux de télévision (ATSC, aux États-Unis). Le seul frein à son utilisation pour un bus interne est lié à la complexité accrue pour décoder le signal et au plus faible niveau de bruit tolérable sans faire d'erreur de lecture.

Par conséquent, PCIe 6.0 sera la première version du protocole à utiliser un code correcteur d'erreurs ce qui est très courant en télécommunications ou même pour le protocole HDMI. En effet, en cas d'erreur de transmission, réémettre les données prendrait trop de temps. L'impact sur la conception de composants PCIe 6.0 est assez direct, vu qu'il faut alors inclure beaucoup plus d'électronique pour décoder le signal (et corriger les erreurs éventuelles).

Source : PCI Express Bandwidth to Be Doubled Again: PCIe 6.0 Announced, Spec to Land in 2021.

Et vous ?

Qu'en pensez-vous ?

Qu'en pensez-vous ?

Vous avez lu gratuitement 251 articles depuis plus d'un an.

Soutenez le club developpez.com en souscrivant un abonnement pour que nous puissions continuer à vous proposer des publications.

Soutenez le club developpez.com en souscrivant un abonnement pour que nous puissions continuer à vous proposer des publications.