Le développement de puces de très grande taille (on parle de plusieurs milliards de transistors) ne peut pas se faire sans simulation : il s'agit de tester, en laboratoire, le comportement de la puce en cours de conception sans devoir la fabriquer. Pour ce faire, on peut utiliser des FPGA, qui fournissent des millions de portes logiques programmables : on peut ainsi tester la puce telle qu'elle sera construite, sans jamais s'approcher d'une salle blanche.

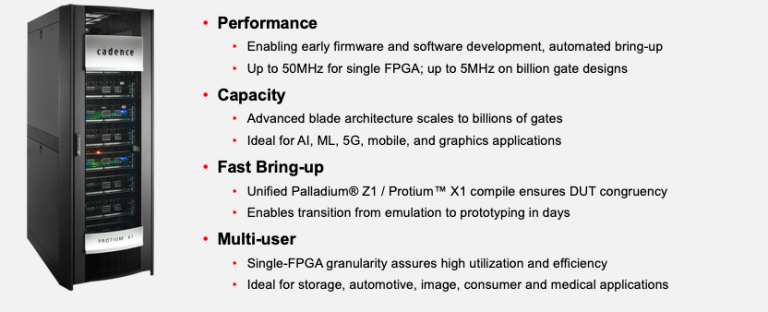

Le développement de puces de très grande taille (on parle de plusieurs milliards de transistors) ne peut pas se faire sans simulation : il s'agit de tester, en laboratoire, le comportement de la puce en cours de conception sans devoir la fabriquer. Pour ce faire, on peut utiliser des FPGA, qui fournissent des millions de portes logiques programmables : on peut ainsi tester la puce telle qu'elle sera construite, sans jamais s'approcher d'une salle blanche. Le principal problème est que les FPGA ne peuvent pas fournir suffisamment de portes logiques pour les puces les plus grandes d'aujourd'hui. Il faut donc soit se contenter de tester des blocs de la puce, soit assembler plusieurs FPGA. Cadence propose désormais une solution intégrée pour ce deuxième choix, Protium X1 : des serveurs remplis de FPGA, qui peuvent tester des puces de plusieurs milliards de portes logiques en assemblant des FPGA.

Ces serveurs peuvent aussi être partitionnés de telle sorte que plusieurs utilisateurs peuvent se les partager. Un seul rack peut ainsi gérer jusque quarante-huit utilisateurs, avec vingt millions de portes disponibles par utilisateur à une fréquence de cinquante mégahertz (si un seul utilisateur dispose du rack entier, la fréquence peut monter à cent mégahertz). L'autre extrême est l'utilisation de plusieurs racks, voire de plusieurs baies, à raison d'un milliard de portes logiques par rack, pour une seule opération de simulation, mais à une fréquence de cinq mégahertz (des optimisations manuelles permettraient de monter au double de la fréquence).

Voir aussi : la page produit.

Source : Cadence Releases Enterprise-Level FPGA Prototyping.

Vous avez lu gratuitement 504 articles depuis plus d'un an.

Soutenez le club developpez.com en souscrivant un abonnement pour que nous puissions continuer à vous proposer des publications.

Soutenez le club developpez.com en souscrivant un abonnement pour que nous puissions continuer à vous proposer des publications.