RISC-V est une architecture qui fait de plus en plus parler d'elle. Elle a commencé comme un projet de recherche académique, mais orienté vers le déploiement : bon nombre de projets de recherche au niveau de l'architecture des processeurs sont volontairement simplistes, mais pas RISC-V. L'université de Berkeley a alors accepté de mettre tous les documents de conception sous licence BSD, c'est-à-dire que cette architecture est entièrement libre : aucune licence à payer à qui que ce soit pour l'utiliser, contrairement à ARM. Depuis lors, le succès de RISC-V est tel que même des sociétés comme Western Digital remplacent toutes leurs puces, notamment ARM, par du RISC-V (même la conception physique de ces puces est libérée). Pour beaucoup, cependant, le risque de changer complètement d'architecture dépasse fortement les économies qu'ils pourraient réaliser

RISC-V est une architecture qui fait de plus en plus parler d'elle. Elle a commencé comme un projet de recherche académique, mais orienté vers le déploiement : bon nombre de projets de recherche au niveau de l'architecture des processeurs sont volontairement simplistes, mais pas RISC-V. L'université de Berkeley a alors accepté de mettre tous les documents de conception sous licence BSD, c'est-à-dire que cette architecture est entièrement libre : aucune licence à payer à qui que ce soit pour l'utiliser, contrairement à ARM. Depuis lors, le succès de RISC-V est tel que même des sociétés comme Western Digital remplacent toutes leurs puces, notamment ARM, par du RISC-V (même la conception physique de ces puces est libérée). Pour beaucoup, cependant, le risque de changer complètement d'architecture dépasse fortement les économies qu'ils pourraient réaliser

SiFive est une société qui gravite autour de RISC-V et conçoit des curs de calcul avec cette architecture ; elle a été fondée par une série de chercheurs derrière l'architecture RISC-V. De fait, les documents initiaux ne permettent pas la réalisation d'un processeur, ils spécifient "juste" l'architecture. À part Western Digital, il n'existe pas vraiment de cur de calcul de relativement haute performance sous licence libre : c'est dans ce marché que SiFive opère, de manière similaire à ARM.

La dernière annonce de SiFive concerne justement un processeur à plus haute performance que les actuels : il est bien plus complexe et peut réordonner les instructions avant de les exécuter. Cela nécessite une grande quantité de transistors pour l'implémentation, mais aussi une analyse fine du comportement du reste du processeur pour savoir quel réordonnancement des instructions permettra d'augmenter l'utilisation du processeur. En effet, quand le processeur récupère une information dans un cache lointain, il peut utiliser ses composants pour effectuer une addition sur deux nombres disponibles dans ses registres, par exemple. Tous les processeurs modernes utilisent des principes de ce genre.

Jusqu'à présent, SiFive proposait deux séries de microarchitectures pour des charges de travail lourdes en 64 bits (contrôleurs pour voitures ou drones, points d'accès WiFi ou 5G, télévisions, etc.) : les U5 et U7, avec une exécution dans l'ordre et un pipeline de longueur variable (à 5 étages pour les U5 et 8 pour les U7, ces derniers étant superscalaires). Les U8 apportent une exécution dans le désordre et un pipeline bien plus profond : 12 étages (par rapport à une quinzaine chez Intel depuis le lancement des Core, par exemple). De fait, en performance, ils peuvent monter bien plus haut : ils peuvent traiter certaines tâches quatre à cinq fois plus rapidement que les U5 et U7.

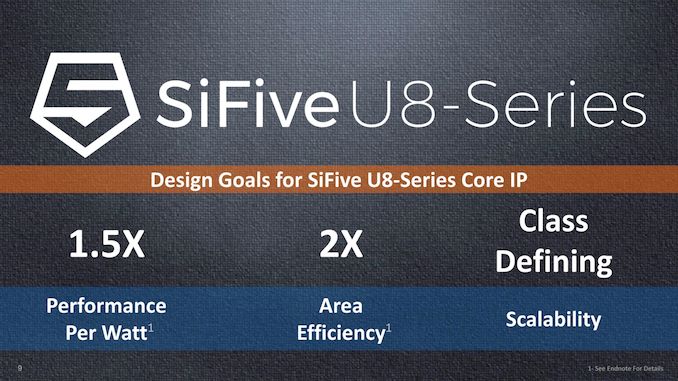

La série des U8 se compare directement aux ARM Cortex A72 : officiellement, elle offre une performance par watt multipliée par 1,5 et utilise moitié moins de surface de silicium. Certes, le A72 n'est pas tout récent, mais les U8 devraient pouvoir entrer en compétition avec les processeurs ARM actuels de milieu de gamme (mais pas avec pareils chiffres). Il semblerait que le haut de gamme ARM ne soit pas encore atteignable, mais cela ne saurait tarder.

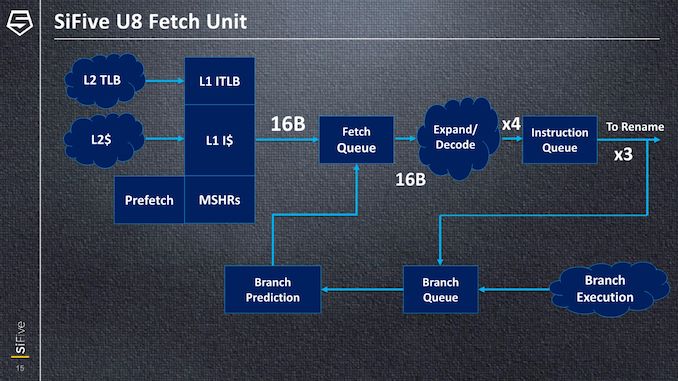

SiFive ne révèle pas tous les paramètres de son architecture (comme les caches), notamment parce qu'elle peut être mise à l'échelle : les différents modèles de la série pourront adopter plusieurs valeurs. Le pipeline général peut gérer trois unités d'exécution simultanément (par rapport à une pour la série U5 et deux pour la U7). À chaque cycle, le cur peut récupérer seize octets d'instructions du cache L1I (les instructions n'ont pas de longueur fixe ) : le décodeur peut gérer quatre instructions simultanément, ce qui correspond à une longueur moyenne d'instruction de quatre octets. Après coup, la file d'attente des instructions ne peut traiter que trois instructions à la fois, une différence rarement vue en pratique (sauf pour la microarchitecture Intel Tremont), qui finiront dans des files d'attente pour chaque partie du cur de calcul (opérations en virgule flottante, sur des nombres entiers ou en mémoire).

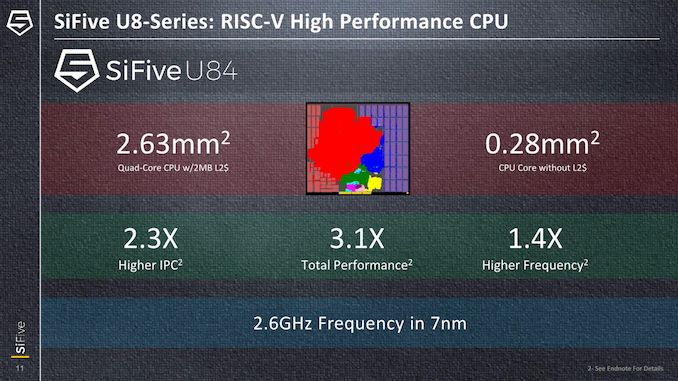

Avec le cur U84, SiFive vise une fréquence de 2,6 GHz avec une lithographie en 7 nm. En omettant les caches de niveau 2, un seul cur devrait occuper une surface de 0,28 mm² ; un processeur de quatre curs et un cache partagé de deux mégaoctets devraient occuper 2,63 mm². En comparaison, un ARM Cortex A55 (dont la performance est approximativement la moitié de celle d'un A72), un cur avec son cache (128 ko) utilise 0,36 mm².

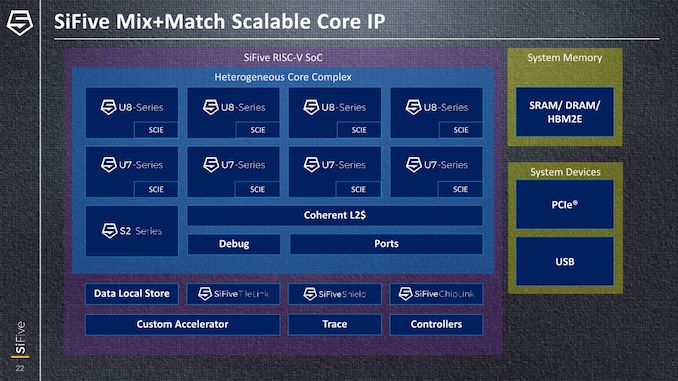

SiFive peut aussi créer des processeurs avec des curs très différents, partageant tous un même cache de niveau 2, pour s'adapter à toutes les situations.

Source : AnandTech.

Vous avez lu gratuitement 38 articles depuis plus d'un an.

Soutenez le club developpez.com en souscrivant un abonnement pour que nous puissions continuer à vous proposer des publications.

Soutenez le club developpez.com en souscrivant un abonnement pour que nous puissions continuer à vous proposer des publications.

.

.

imagine ce futur complètement open source ou chaque application ne peut fonctionnement que sur la machine ou elle a été compilé ^^

imagine ce futur complètement open source ou chaque application ne peut fonctionnement que sur la machine ou elle a été compilé ^^