Depuis plus dune décennie, le paradigme principal pour la conception de puces électroniques était dassembler une série de transistors sur un plan. Ainsi, par exemple, Samsung est passé dune technologie 120 nm en 2003 à du 16 nm en 2014, avec une amélioration chaque année au niveau de la finesse de gravure, en moyenne. Cependant, les améliorations se font au prix de processus de plus en plus compliqués, notamment au niveau de lexposition des circuits : pour dessiner les transistors, un laser est utilisé à travers un masque, avec différents processus optiques pour atteindre les finesses de gravure actuelles (de nouvelles techniques sont en cours dexploration, comme les EUV). Actuellement, les processus les plus avancés utilisent une exposition en quatre phases, ce qui nécessite une préparation des galettes de silicium en amont de plus en plus coûteuse : les étapes de dépôt et dattaque chimique de la surface représentent maintenant les deux tiers du coût de fabrication dune galette.

Depuis plus dune décennie, le paradigme principal pour la conception de puces électroniques était dassembler une série de transistors sur un plan. Ainsi, par exemple, Samsung est passé dune technologie 120 nm en 2003 à du 16 nm en 2014, avec une amélioration chaque année au niveau de la finesse de gravure, en moyenne. Cependant, les améliorations se font au prix de processus de plus en plus compliqués, notamment au niveau de lexposition des circuits : pour dessiner les transistors, un laser est utilisé à travers un masque, avec différents processus optiques pour atteindre les finesses de gravure actuelles (de nouvelles techniques sont en cours dexploration, comme les EUV). Actuellement, les processus les plus avancés utilisent une exposition en quatre phases, ce qui nécessite une préparation des galettes de silicium en amont de plus en plus coûteuse : les étapes de dépôt et dattaque chimique de la surface représentent maintenant les deux tiers du coût de fabrication dune galette.Cependant, cette manière de procéder doit évoluer, notamment à cause des difficultés à faire progresser les technologies dimpression de circuits tout en maintenant des coûts raisonnables. Pour ce faire, une technique actuelle est de combiner plusieurs circuits dans une même puce, comme le font déjà AMD et NVIDIA pour leurs processeurs graphiques (pas tous, loin de là !) ou encore Altera : la partie mémoire HBM2 est superposée au processeur principal.

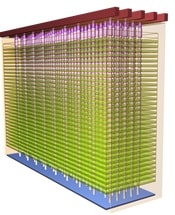

De son côté, Samsung va encore plus loin : dès 2014, le fondeur coréen pousse lidée de superposition encore plus loin pour ses composants de mémoire. Une telle puce est composée de trois types de couches :

- une couche CMOS pour toute la partie auxiliaire du composant, les contrôleurs ;

- plusieurs couches formant un tableau de mémoire, là où les valeurs sont effectivement stockées ;

- une structure dinterconnexion entre les deux types de couches.

Les contrôleurs et linterconnexion sont des couches planaires tout à fait traditionnelles, alors que la mémoire proprement dite exploite un procédé tout à fait spécifique, en trois dimensions schématiquement, un film de silicium est déposé, puis une première couche de transistors est créée, lopération est répétée un grand nombre de fois. Linformation est alors stockée le long dune chaîne de cellules, au lieu dune seule cellule : pour en agrandir une, il suffit de déposer un plus grand nombre de couches.

Pour les chiffres, la densité peut beaucoup augmenter : par rapport à quelques mégaoctets par millimètre carré en 2003 à plus 1,1 Go en 2014 à raison de trois bits par cellule, la première génération 3D ne montait quà 0,97 Go le millimètre carré, en 2014, avec deux bits par cellule et vingt-quatre couches. Depuis lors, le processus saméliore : en 2015, avec trente-deux couches, il était possible de stocker trois bits par cellule (1,86 Go/mm²) ; cette année, en montant à quarante-huit couches, la densité monte à 2,62 Go/mm², toujours avec trois bits par cellule. Dans le futur, de nouvelles couches devraient sajouter, avec à lhorizon 2020 cent vingt-huit couches, quatre bits par cellule, pour une densité de 8,67 Go/mm² (plus de huit fois la densité actuelle).

Actuellement, la technologie de Samsung reste relativement expérimentale, elle nest pas prête pour la production de masse : les rendements sont relativement faibles, mais samélioreront avec lexpérience. Micron planche sur des techniques similaires et, daprès les premières expériences, une production avec trente-deux couches serait vingt-cinq pour cent moins chère par bit mémorisé que le même composant en technologie 16 nm. Les coûts de production dune galette augmentent, mais il semblerait que ce soit dans des proportions raisonnables.

Source (dont image) : 3D NAND Moores Law in the third dimension.

Ce contenu a été publié dans Matériel par dourouc05.

Vous avez lu gratuitement 1 559 articles depuis plus d'un an.

Soutenez le club developpez.com en souscrivant un abonnement pour que nous puissions continuer à vous proposer des publications.

Soutenez le club developpez.com en souscrivant un abonnement pour que nous puissions continuer à vous proposer des publications.